干货 如何高效利用逻辑分析仪存储器

存储深度是逻辑分析仪的一个重要参数,在传统模式下,存储深度×采样分辨率=采样时间,这意味着在保证采样分辨率的前提下,大的存储深度直接提高了单次采样时间,即能观察分析更多的波形数据;而在保证采样时间的条件下,大存储深度则可以提高采样频率,观察到更真实的信号。

在测试过程中,我们都希望逻辑分析仪的存储深度能够越大越好,这样就能达到鱼与熊掌两者兼得的效果。但当逻辑分析仪存储深度是有限的,我们要做的,便是高效利用逻辑分析仪存储器。

从推出逻辑分析仪开始,广州致远电子有限公司就采用了创新的Timing-State模式,该模式可以看作是利用一种数据压缩技术来达到延长记录时间的目的,其理论最大压缩比为无穷大,在存储容量不变的条件下,极大的提高了记录时间。

如图1所示为逻辑分析仪的采样时序图,图中共表示了22个采样点,按照传统的记录方式需要22个存储单元来记录采样数据;而Timing-State数据跳变存储技术记录的是数据的状态和状态的持续时间,只需要8个存储单元;因此在存储容量不变的条件下,我们可以极大的提高记录时间。

在某些特殊场合,信号线上的数据变化速率跨度较大,因为有高速数据的存在,采样频率必须尽可能的高,这像是一把双刃剑,在提高了采样分辨率的同时减少了单次采样的记录时间。比如UART数据,在大多数时刻,信号线上是处于空闲状态的,只有在极少数情况下才会有数据。如果使用普通存储模式,逻辑分析仪只能存储触发点前后很少的数据,这是因为在空闲时长时间不变的信号会迅速填充满存储器。而如果采用跳变存储技术,在空闲时因为信号线上没有跳变信号,所以并不占用存储空间,这样总的存储时间就会提高。

在复杂的系统环境中,总线上总是不断的传输高速数据,要记录分析这些数据,通常有两种途径:一是增加足够的存储器,将整个过程完整的记录下来(如果有可能的话),对于工程师来说,如何处理这些数量惊人的数据同样是个难题;另一个途径是只在希望的数据出现时才存储,而其他数据则看作是无用的。

在LAB7000系列逻辑分析仪中,加入了独具特色的条件存储技术,其设计初衷就是减少工程师分析复杂系统的难度,合理的设置可以让工程师只看自己关心的数据,同时因为其对不关心的数据采取视而不见的态度,存储器的利用率也会提高。

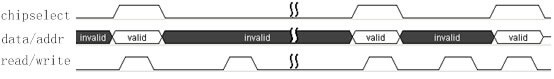

图2为一个典型的MCU对外设的读写操作过程,当测试某一外设时,通常只关心对该外设的读写操作,而对于MCU和其他外设的数据交换,可以置之不理。这时可以用到带使能控制的采样方式,利用chipselect信号作为使能标志。LAB7000系列逻辑分析仪可以针对使能信号有效的标志来存储数据,而在使能无效的时间内,只记录时间信息。

除了单通道存储深度高达到128Mbits外,LAB7000系列逻辑分析仪的其他存储特点同样是独树一帜的, Timing-State模式继续保持对低速数据的记录时间优势,同时新加入的条件存储功能在分析大批量数据时更能快速直观的定位目标信息,减少了用户的分析时间同时也提高了存储器的利用率。