电路板阻抗原理知识及应用

我们做电子设计,遇到高速电路时会遇到很多问题,也会有很多新名词,比如:过冲,下冲,时延,阻抗,反射等,经过我的反复思考与研究,得到一些心得,跟大家一起分享。

随着信号传送速度迅猛的提高和高频电路的广泛应用,对印刷电路板也提出了更高的要求。印刷电路板提供的电路性能必须能够使信号在传输过程中不发生反射现象,信号保持完整,降低传输损耗,起到匹配阻抗的作用,这样才能得到完整、可靠、精确、无干扰、噪音低的传输信号。

在高速数字电路的PCB设计上,我们设计的产品不管是用到DDR2,还是DDR3内存,不管是PCIE差分还是SATA传输,都用到了高速PCB设计技术,而我们所设计的PCB用了阻抗控制技术后,基本上没有出现是PCB问题跑不通的情况。要理解高速信号的设计知识,先要从一些基础电子知识说起。

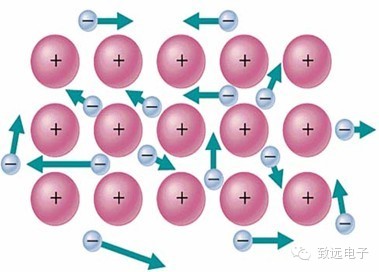

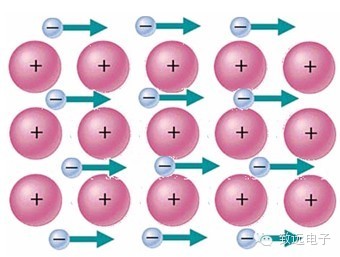

导体中的自由电子在电场的作用下定向移动形成电流。电流方向只是物理学中约定俗成的一个规定,物理上规定电流的方向是正电荷的定向移动的方向或者负电荷的定向移动的反方向。电流的速度不是电子运动速度,而是电场的速度。

电信号的传播速度是与导体周围的介质介电常数有关的,电信号在真空中(指导体周围比较大的范围内都是真空)的传播速度是光速3*10^8 m/s,换算为30 cm/ns 。在其它的介质中,它的传输速度是不一样的,如果相对介电系数是 Er ,则传播速度为 30/Er^0.5。例如,在水中,水的相对介电系数是80,所以,传播速度约是真空中的1/9 ,即: 30/80^0.5 = 3.35 cm/ns。在PCB中,FR4的相对介电系数约为4,所以,传播速度是真空中的一半,即:30/4^0.5 = 15 cm/ns。

传输线的特征阻抗,又称为特性阻抗,是我们在进行高速电路设计的时候经常会提到的一个概念。信号在传输线中传输的过程中,在信号到达的一个点,传输线和参考平面之间会形成电场,由于电场的存在,会产生一个瞬间的小电流,这个小电流在传输线中的每一点都存在。同时信号也存在一定的电压,这样在信号传输过程中,传输线的每一点就会等效成一个电阻,这个电阻就是我们提到的传输线的特征阻抗。这里一定要区分一个概念,就是特征阻抗是对于交流信号(或者说高频信号)来说的,对于直流信号,传输线有一个直流阻抗,这个值可能会远小于传输线的特征阻抗。一旦传输线的特性确定了(线宽,与参考平面的距离等特性),那么传输线的特征阻抗就确定了。一般的PCB走线特征阻抗计算公式: Z0≈ (L/C)^0.5

其中L是单位长度传输线的固有电感,C是单位长度传输线的固有电容。通过这个简单的计算公式我们能看出来,要改变传输线的特征阻抗就要改变单位长度传输线的固有电感和电容。

根据以上公式,这样我们就能更好的理解影响传输线特征阻抗的几个因素:

- a. 线宽与特征阻抗成反比。增加线宽相当于增大电容,也就减小了特征阻抗,反之亦然。

- b. 介电常数与特征阻抗成反比。同样提高介电常数相当于增大电容。

- c. 传输线到参考平面的距离与特征阻抗成正比。增加传输线与参考平面的距离相当于减小了电容,这样也就增大了特征阻抗,反之亦然。

- d. 传输线的长度与特征阻抗没有关系。通过公式可以看出来L和C都是单位长度传输线的参数,与传输线的长度并没有关系。

- e. 线径与特征阻抗成反比。由于高频信号的趋肤效应,影响较其他因素小。

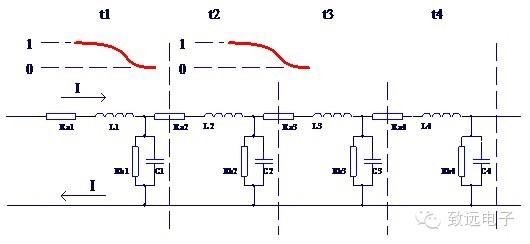

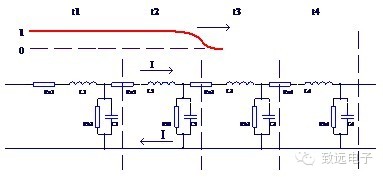

下面再以图示的方法说明下,传输线是一个分布参数系统,它的每一段都具有分布电容、电感和电阻。传输线的分布参数通常用单位长度的电感L和单位长度的电容C以及单位长度上的电阻、电导来表示,它们主要由传输线的几何结构和绝缘介质的特性所决定的。分布的电容、电感和电阻是传输线本身固有的参数,给定某一种传输线,这些参数的值也就确定了,这些参数反映着传输线的内在因素,它们的存在决定着传输线的一系列重要特性。传输线的等效电路是由无数个微分线段的等效电路串联而成。

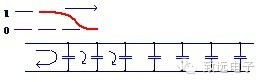

在上图里,以t1时间段来说,电阻Ra1的阻值很小,电感L1也很小,电容C1也很小,电阻Rb1很大。电信号从低电平变高电平高电平,它不是整条导线上一下子就变为高电平了,而是像钱塘江大潮涨潮或波浪推进时,是有一个过程的。钱塘江大潮来后,就把江面从低水位变到高水位了,波浪是一个一个的来,就像高频信号不停的传输。信号电场也如潮水一样,它是后面的推前边的,前面的继续向前。

在导线上的一个固定地点,它的电平是如潮头逐渐上升的,这个上升的波形,就是我们平常可以用示波器测量的上升沿,这个上升沿有快有慢,高速信号,需要上升沿和下降沿都要快,否则电平还没到,下一个信号电平又来了。而低频信号并不等于上升沿下降沿就平缓,它也可以比较陡。低频信号如果上升沿和下降沿比较陡的,也要当高频信号来处理。

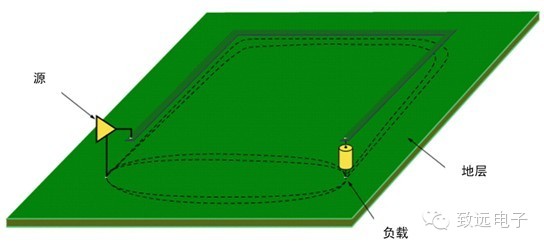

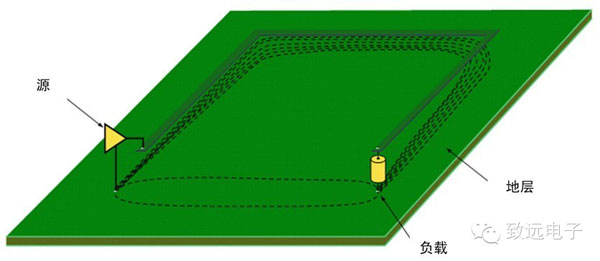

我们可以这样来简单理解信号传播与信号回路问题,一个信号在导体里传播,它就要受到导体上电阻的衰减,电感的阻碍,给寄生电容充电和介质漏电等。微分导线后可见,信号峰头到这里来后,由于给寄生电容充电和介质漏电,它就会沿传播路径下的参考平面有一个返回电流,然后到下一个微分点,电流又返回到前一个点,这个信号还未传到终点前,沿导线的传播路径的返回电流一直存在,等信号到达终点后,整个通路建立平衡后,返回路径才从信号最好走的(最短路径,最小电阻)路径返回。

低速信号的信号峰头从始点到终点的时间和高速信号一样,但它两个信号间时间比较长,信号推进时从导体路径返回电流,平衡后从最短路径返回。而信号峰头从始点到终点的时间远小于信号周期,所以大部分电流从最短路径返回了。

高速信号和低速信号不一样,它的波形一个接一个的,所以绝大部分返回电流从信号传播路径返回。

前面说过,在FR4的相对介电系数为4的PCB中,信号传播速度是约为15 cm/ns。如果我们以15cm长的导体来传信号,信号从这头传到那头就要1ns的时间,一个500MHz的时钟信号在里面传播,就是一个波的峰头还没到,第二波形又发出去了。这样一个波一个波的传过去,返回的电流一直从传播路径上走。

信号传播,也相当于在给沿途的寄生电容充电,寄生电容的负端就有返回电流了。

我们为什么要讲返回路径,返回路径是信号传播的原动力,只有让返回路径畅通,信号传播途中才有电压差,才使信号向前走。所以返回路径是电子电路必不可少的,是设计PCB特别是高速电路一定要考虑的,否则,就有串扰,反射,过冲,波形畸变等各种情况产生,电路工作不正常。返回路径就是参考面,参考平面是阻抗的一大因子。

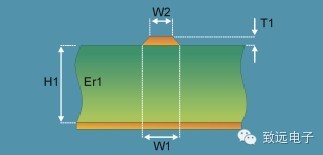

在下图中,是单端导线的截面图,阻抗与H1成正比,与Er成反比,与W1、W2、T1成反比,大家可以看出,W1,W2,T1是一个梯形面,这三个参数组成的就是导体截面,实际阻抗与导线截面积成反比。也就是说,特性阻抗是与导体截面积、导体到参考平面的距离和导体到参考平面间介质的介电常数有关的。

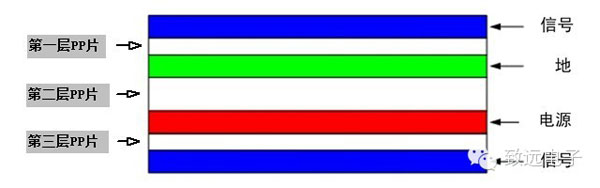

我们在设计PCB板时,设计好参考平面,如四层板,中间两层是参考层;六层板,第二层和第五层是参考层。参考平面可以是地层,也可以是电源层,以地为参考层更好。

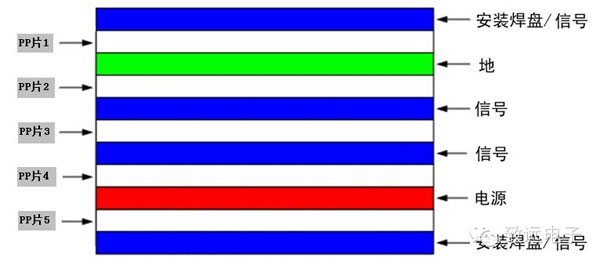

六层板的第一层和第三层以第二层为参考平面,第四层和第六层以第五层为参考平面,要使第三层和第四层相互影响较小,可以把PP片3的厚度加大,厚度加大到远远大于(三倍以上)PP片2的厚度时,它们间的影响就非常小了。如PP片2和PP片4的厚度为3mil,PP片3的厚度为10mil,这时,你用阻抗计算软件算第三层或第四层信号线的阻抗,你用微带线和带状线的模型去计算,计算的结果相差不大。

用这个比喻大家就明白了,月亮到地球的距离是38万公里,地球到太阳的距离是1.5亿公里,太阳的质量和体积都比地球大得非常多,但对月球的影响远远不及地球,原因就是月亮到地球的距离远远小于到太阳的距离。所以大家在对待多层数复杂电路板的时候,找好一个参考层,让其它层远离这个信号层,让指定的这个参考层为主影响,这时,我们设计的阻抗叠层模型就要简单很多。

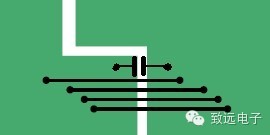

参考层要完整覆盖信号走线,中间断面或打孔过多造成隔断,都会严重影响信号传输质量。但很多时候为了成本考虑用合理的层数,信号要换层,参考面也可能是两个电源平面,中间是分断的,这时就要有方法处理下。信号线换层时,也要考虑返回电流的回路,所以参考层变了,也要把回路联通,对于参考层不是一个电平的,要在两个电平参考层间加电容连接,如下图:

参考层变化了,阻抗就就变了。参考层电平不一样,又不能直接连通,这时就加电容来连接。电容有通交隔直的作用,在两个不同电平的参考面间加电容,给高频信号一个返回通路,也使阻抗不连续变好一些。

上面讲了一部分阻抗设计知识,当然这些知识是我们平常很少注意的地方,也从另一个侧面来理解阻抗。要彻底搞懂阻抗知识及用好它,我们还有很多知识点需要补充,这些知识点很容易在书本上看到的,也要花很多功夫学习。

做PCB设计,把元件布好和连接好导线只算低层次。要想你设计的电路板可靠地工作,还有非常多的知识要补充学习,再灵活应用。。

简单的设计方法,也可以让你设计的高速PCB电路达到阻抗要求

你不想搞懂高深的理论知识,下面说一下简单的设计方法,也可以让你设计的高速PCB电路达到阻抗要求。你在设计PCB时,单端信号线走线宽度设置成一个宽度,差分(双端)走线设置为另一宽度,电源线等过电流的线按电流要求又设置成其它宽度。根据经验,如单端线宽设为5mil,差分的设为4.5mil,线间距都为5mil,当然还要考虑参考平面。这样,你在发板要求里给生产厂家说明,说:线宽为5mil的都给做成50欧姆阻抗,线宽为4.5mil的为差分线,做成100欧姆阻抗就行了。这里说明的是每种阻抗做一种宽度,生产厂家就会按你的要求给你计算生产成你要的阻抗要求了。当然,你做的线宽还是要先用阻抗计算软件计算下,误差大了,生产厂家给你调整不了的。

简单说明就是,你是不同的阻抗用不同线宽,他们就会把这个线宽选择出来调整,他们可以改变线宽、线间距、介质材料、铜厚度、介质厚度等来满足阻抗要求。在设计之前也要多和厂家沟通,调整设计元素,减少厂家的调整难度。

致远产品从低速到高速,从单机产品到复杂产品,以致今天我们做高端仪器仪表,是我们十几年里不断的摸索学习,下了很多心力,才在高速复杂电路上有所建树。今天我们的高端仪器,有高速FPGA,高速DSP,DDR2/DDR3多内存组成的大系统,我们能使它稳定可靠的工作,全靠这些理论知识加实践经验结合。如我们做了气体分析记录仪器,单板用了22片DDR内存,我们PA系列功率分析仪,板卡内是DSP+FPGA组成的复杂系统,板卡间跑PCIE高速信号,这些都靠我们的扎实丰富的理论加实践知识去完成的。

任何一门知识都不是单独存在的,它都和其它知识组成系统知识,只有在相关知识上都了解情况下,再融合贯通,灵活应用,才能做出好的作品来。