M28X PCB设计指导

I.MX28系列是飞思卡尔Arm9™系列处理器的新成员,集成了显示、电源管理、CAN、USB和以太网等连接功能,可为各种成本敏感型的应用降低了系统成本和复杂性。针对其在PCB设计方面,我们总结了一些方法和经验,欢迎大家借鉴和指导。

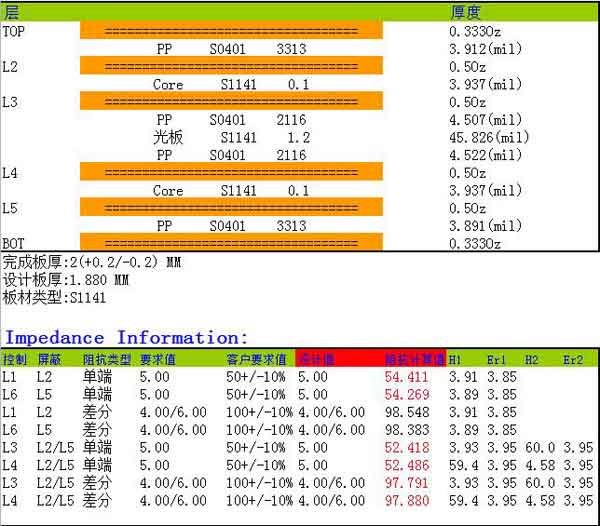

推荐的叠层(适用于6层板):

1) L1(TOP,信号)- L2(地平面)-L3(电源平面、少量信号)-L4(信号)-L5(地平面)-L6(BOTTOM,信号)

L3,L4在RAM部分可走信号,BOOTOM走1.8V电源;CPU部分L3可敷电源。优点是有两个地平面,有较好的EMC性能和信号完整性。但L3只能走少量信号,需要配合底层扇出,可能需要增加更多的过孔进行换层。

2) L1(TOP,信号)- L2(地平面)-L3(信号)-L4(信号)-L5(电源平面)-L6(BOTTOM,信号)

此叠层适合信号比较交叉的情况,保证L3,L4皆可出线。L5电源平面进行了分割,相对上述叠屋在一定程度上电源完整性会更好一点。顺便提一下的是要留意L4,L6的重要信号不要跨电源平面走线。

推荐的走线、叠层

单端:5mil

差分:4/6mil(线宽4mil,间距6mil)

叠层设计可参照下图所示,对于L1,L3,L4,L6的阻抗有较好的控制。

过孔:可使用8/16mil或者10/16mil。该过孔大小刚好符合CPU内5mil走线的扇出。

4层走线可参考官方指导手册的扇出方法。注意使用4层板的话,需要走线的空间相对较大,而且底层信号走线较多,会影响滤波电容等的放置,会大大削弱信号完整性和EMC性能。对于要求较高的场合例如工业环境下,尽量还是使用6层及以上的设计。

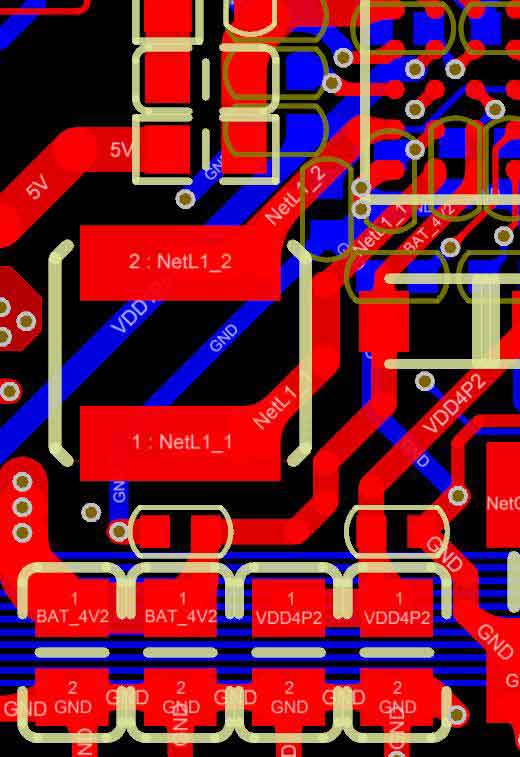

DCDC_GND PIN(A17)至少有两个过孔到地平面,可减少开关电源产生的噪声。

DC-DC电感尽可能放置与CPU同一面,且尽可能靠近CPU,这样可避免走线过长和使用过孔。如果电感一定要放反面,则必须通过多过孔进行连接。

DCDC_BATT PIN (B15)的输入电容尽量靠近PIN脚放置,保持走线不长于5mm。

以下布局和走线供参考(由于结构的限制,DCDC_BATT的电容放置得较远):

滤波电容必须靠近电源脚放置,包括DCDC_VdivIO, DCDC_VdivA, DCDC_VdivD。

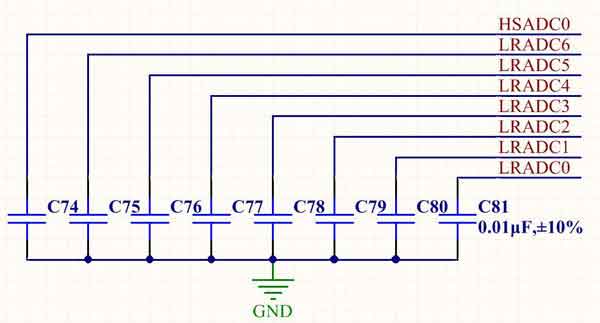

LRADC和HSADC的各个信号都需要接0.01uF的电容,该电容须靠近CPU放置,并远离DCDC和其他数字电路(或者用地线隔开)。HSADC包地。

滤波电容放置的例子(包括CPU电源的电容):

晶振电路比较敏感,靠近CPU放置,走线尽可能短,并用地线保护起来。

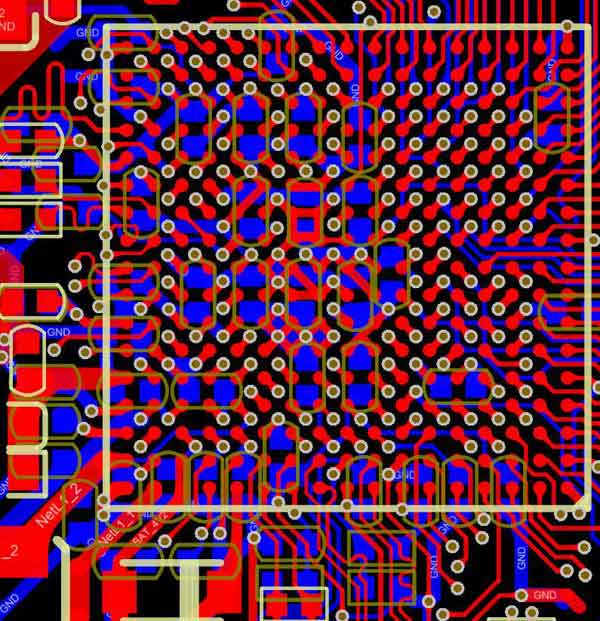

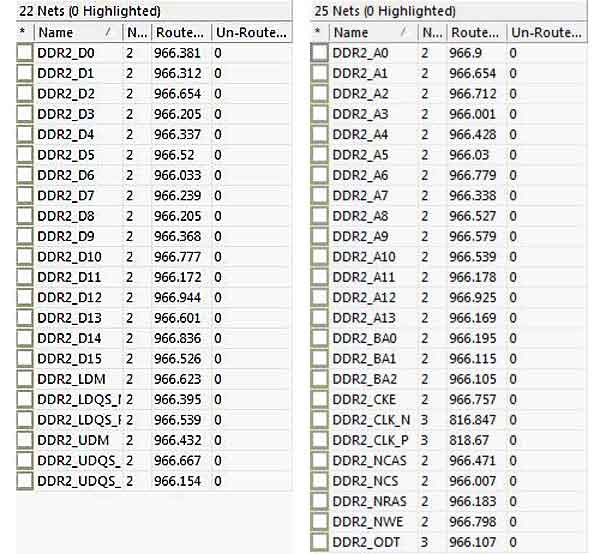

地址/控制信号:长度差控制在200mil;

时针CLK:差分长度差控制在5mil;

数据DQ/数据掩码DQM:长度差控制在100mil;

数据选取DQS:差分对长度差控制在5mil;长度与DQ匹配。

以上信号单端阻抗为50-60欧姆,差分阻抗为100欧姆。地址和数据线之间不要交叉走线。可能的话同组的信号尽量使用相同的层。

VREF尽可能用比较宽的线。

有条件的话RAM各信号长度匹配越精确越好,以下例子是严格等长的(因为CLK差分上有串联的匹配电阻,实长会比表格显示的数值大),供参考。

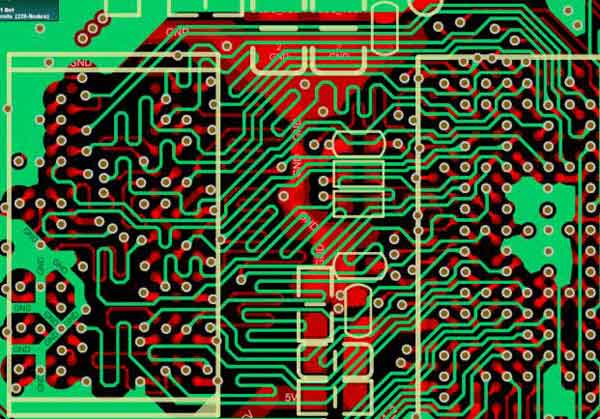

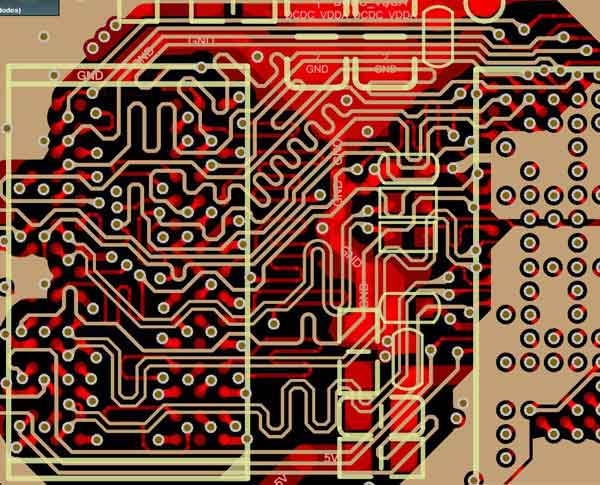

参考例子(分别为CPU与RAM之间的L3,L4走线,BOTTOM层已隐藏):

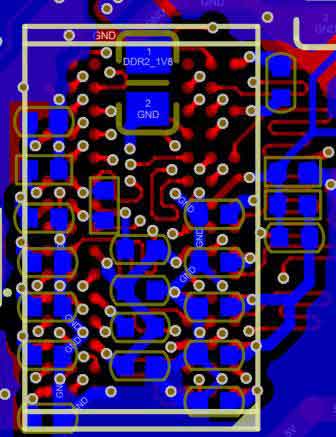

RAM的1.8V电源PIN,滤波电容要靠近放置,保持每个电源PIN和GND至少有一个过孔。

如下图:

差分信号等长走线,长度差控制在5mil;阻抗约90欧姆。走线与其他信号要隔开一定的距离,约20mil以上。也可包地处理。注意其信号不要跨越不同的地/电源平面,可保证其信号质量,以避免其他EMI问题。

TX/RX差分长度差控制在5mil;差分阻抗为100欧姆。且其与板边距离须1in以上,提高其辐射抗扰度。

TX与RX之间保持一定的距离,至少30mil以上。

49.9欧的上拉电阻尽量靠近接口放置,连线尽量短,不要超过400mil。

以太网变压器两端要进行隔离处理,包括信号和地(适用需要外接变压器的情况)。

1.CPU直接引出且靠近板边、外壳、按钮、接口等的信号,比较敏感,特别是做ESD测试时很容易引入干扰,所以要做保护处理。比较好的情况下是增加防护器件,兼顾成本的情况下至少也要作包地处理,靠近CPU附近位置要添加一小电容或者RC滤波。

2.电源平面进行分割的时候,不要让邻近层的重要信号,特别是有阻抗要求的信号跨越不同的平面。否则会影响其信号的完整性。

3.M28X芯片自带的DC-DC电路,其引脚的分布刚好与模拟、复位、晶振、USB等重要信号相邻,在布局上可能会造成一定的困难。建议DC-DC、晶振电路的元件与CPU放置同一层,走线可直连,且减少了大量的过孔,可空出很多空间放置小电容与及其他信号的扇出。另外走线的时候建议每一层都用地线将以上信号分别包起来,避免互相影响。

4.1.8V、3.3V电源由M28X内部直接产生,所以尽量采用敷铜的形式,且CPU背面尽可能每个引脚都添加至少一个滤波电容,保证其电源的完整性并往外部供电。留意并避免CPU内部大量的过孔可能会切断其电源平面的完整。

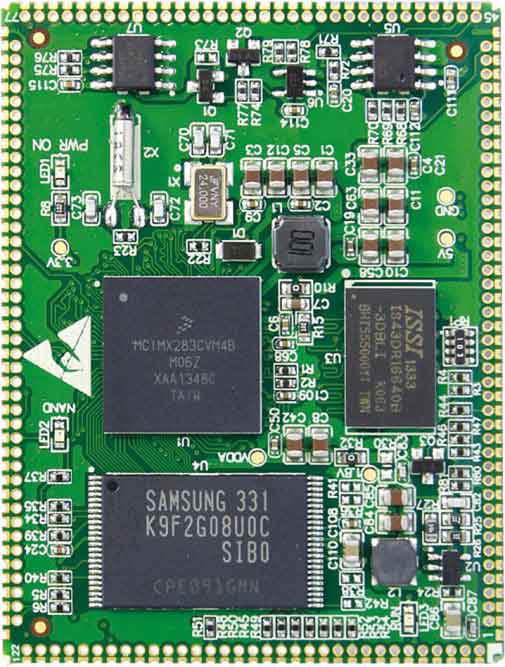

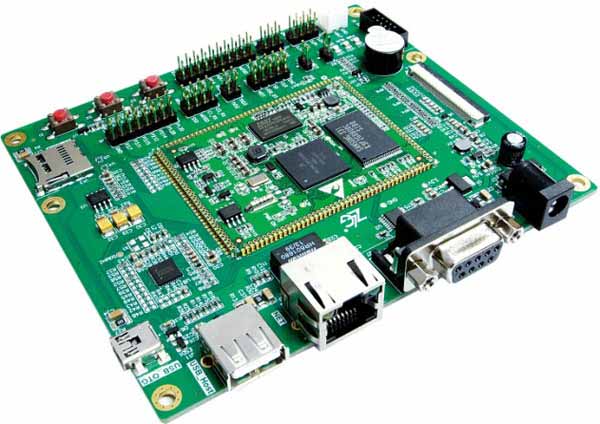

我们用上述方法,完成M283的核心板设计。核心板采用四周是邮票孔方式和外界连接,也可以使用1.27的排针相连。然后配置一个底板,就组成了一个可用的学习板或工控板了。

经过我们测试,整个板所有接触静电放电8KV, 耦合放电15KV ,可见整个板的抗干扰能力是非常强的,作为工业控制用也是满足要求的。

带液晶屏的工控学习板模样,在淘宝上有卖,才258元,真是免费的Arm9™学习平台。