DDR学习笔记

摘要的描述相信大家都深有体会,最近闹得沸沸扬扬的南京贴吧里的《南京珠江路百脑汇就是骗子窝》和网上相关微博《珠江路的骗子,你们还能活多久》等都无情的揭露着电子消费市场的黑暗面,身处其间的我们又该如何练就慧眼,确保自己买到称心的爱机呢,也许我们可以先从内存说起。

图 1鱼龙混杂的电脑城

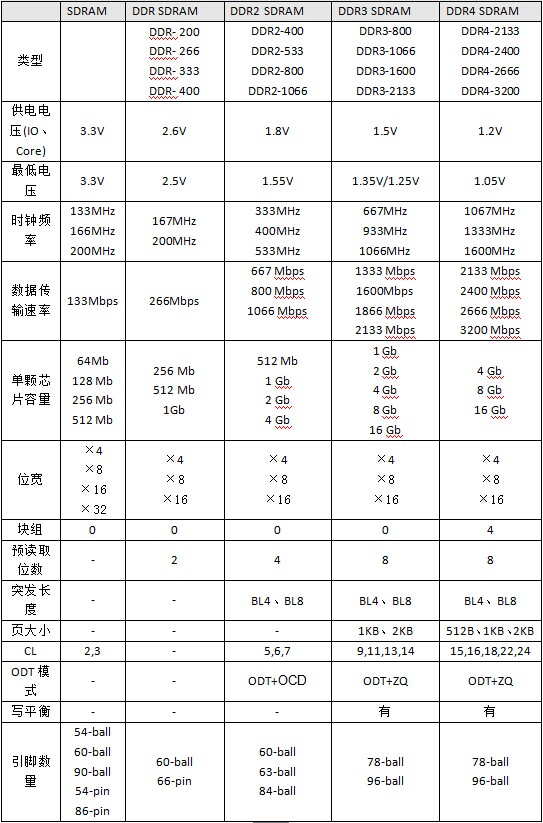

1.什么是DDR?

DDR,全称:DDR SDRAM ,Double Data Rate Synchronous Dynamic Random Access Memary,即,双数据速率同步动态随机存取记忆体,也就是我们常用的内存,它从SDRAM的基础上发展起来,以后依次出现了DDR SDRAM、DDR2 SDRAM、DDR3 SDRAM、DDR4 SDRAM。它们的能效不断提升。文章结尾附一张纯良心内存能效参数表。

图 2DDR家族的一员

2.1SDRAM

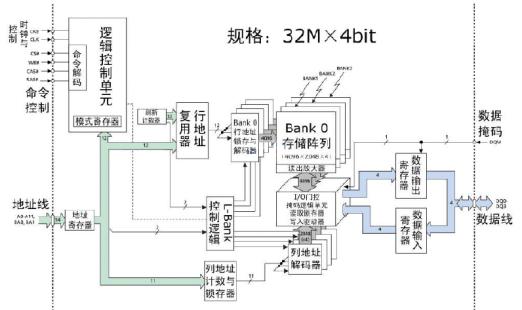

SDRAM内部组成如,可见其组成可以分为几个部分,存储阵列、IO门控单元、行列地址解码器、行列地址锁存器、逻辑控制单元(包含模式寄存器)、数据输入输出寄存器等。

图 3SDRAM结构图

存储矩阵内部结构,以8位内存单元为例,每个内存单元的数据输出是并联在一起,通过行列地址线选中一个存储单元,

图 4存储单元结构图

存储容量大小和数据位宽度、行地址、列地址、块数量等的关系

2.2DDR SDRAM

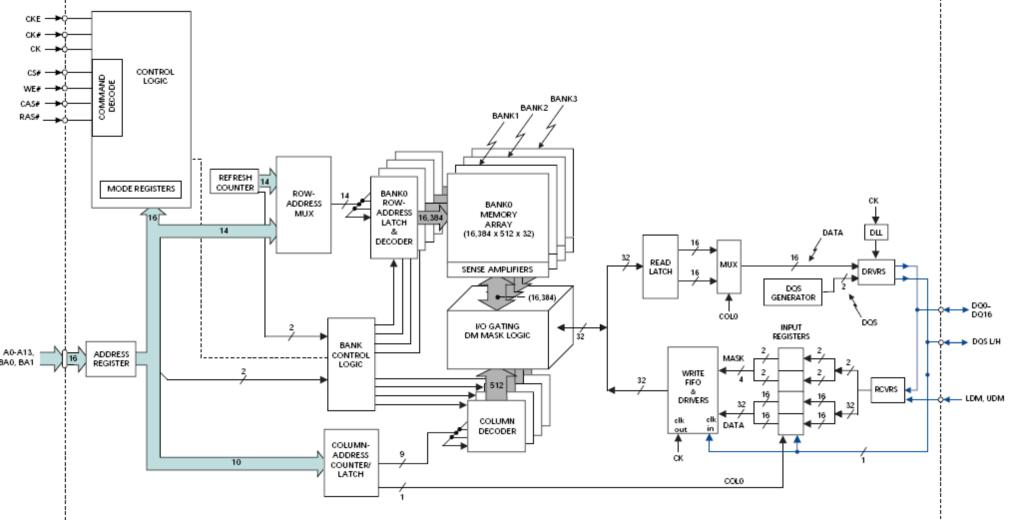

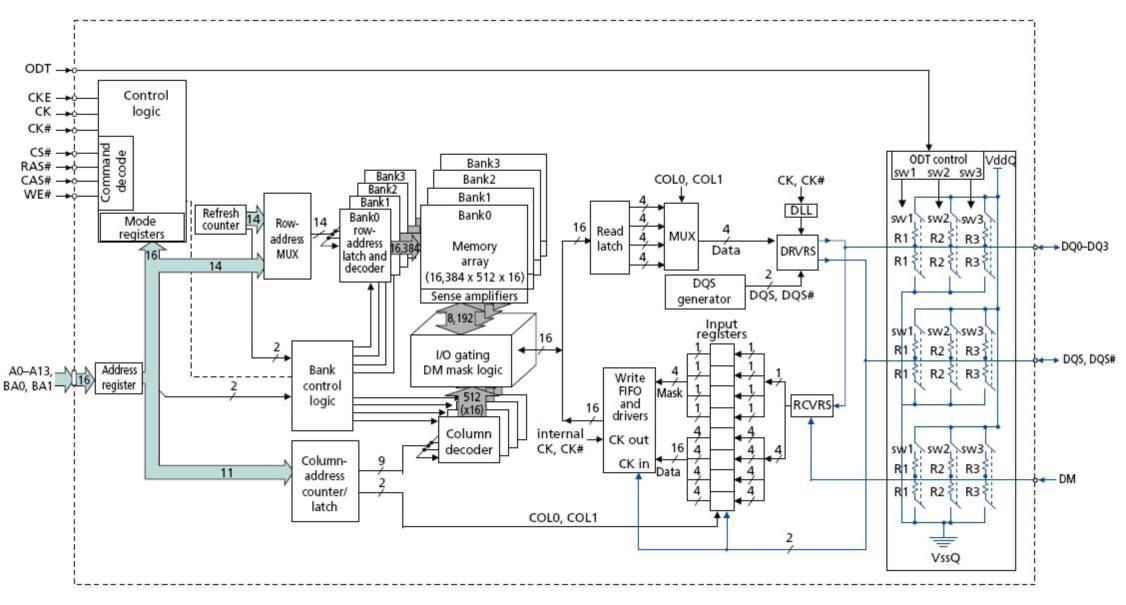

图 5DDR SDRAM 结构图

DDR的内部结构与SDRAM相比,数据读写部分改进比较大。其一,使用了两位预读取的技术;其二,增加了DLL(delay lock loop演示锁定回路);其三,增加了数据掩码控制和数据总线反转控制;此外,时钟信号和数据选通信号改为差分信号。

2.3DDR2 SDRAM

DDR2 SDRAM整体布局变化不大,在输入输出数据总线接口上变化比较多。

图 6DDR2 SDRAM结构图

DDR2在DDR的基础上增加了ODT(on-die termination片上终结,即通过内部逻辑选择合适的终端电阻进行匹配)功能,预读取提高到了4位,即每传输4个字节/字,只有第一个字节/字有潜伏期。

2.4DDR3 SDRAM

DDR3 SDRAM在输入输出数据总线接口上继续提升性能,在存储结构上改进工艺,堆叠更多的存储块,提高单颗芯片的容量。

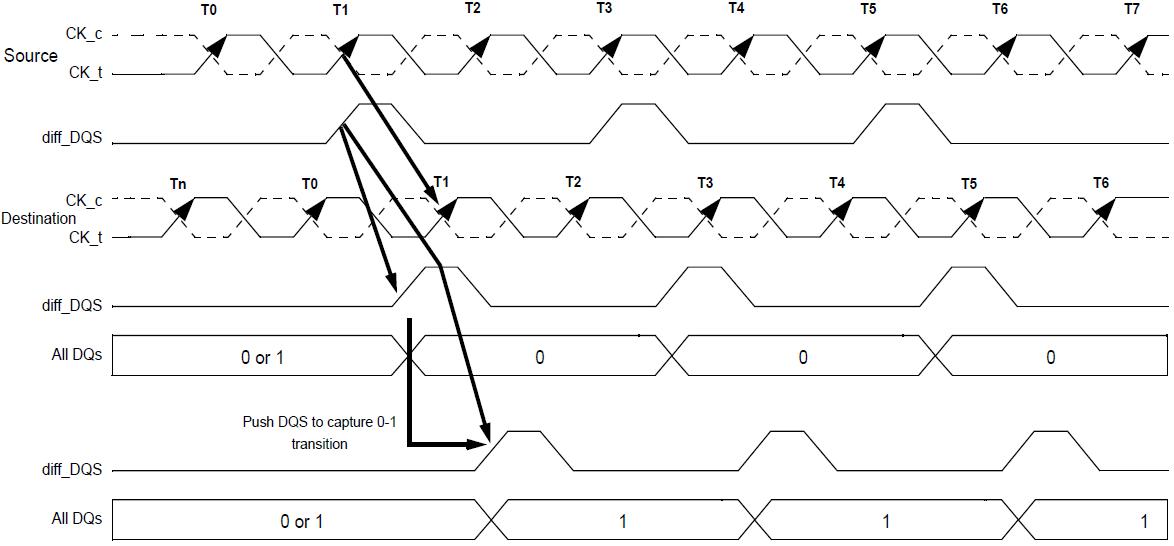

在功能上的改进有,增加了读写平衡功能。

图 7读写时序平衡关系

2.5DDR4 SDRAM

DDR4 SDRAM在输入输出数据总线接口上继续改善性能,在存储结构上继续改进工艺,不仅堆叠更多的存储块,而且使用硅片穿孔工艺把把堆叠成的存储块进行并列放置,集中到一颗芯片中,提高单颗芯片的容量。

图 8DDR4 SDRAM

2.6结尾与附录

以上便是关于DDR的几点小知识,站在理论的制高点,结合网上相关防伪攻略,能让我们更有效的维护自身权益。

篇首说的那张内存参数能效表,请拿好

表 1内存参数表